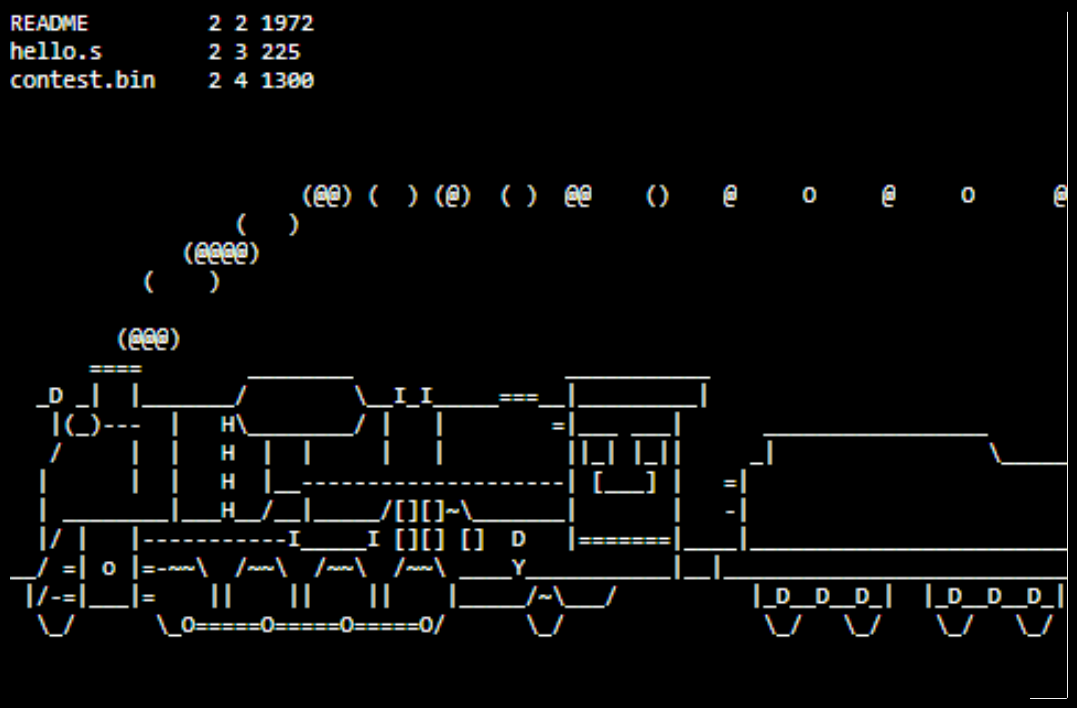

The homemade processor works with a homemade tool chain

A few years ago, [Takaya Saeki] and other students at the University of Tokyo received very limited instruction during their "CPU drill" class, like:

Take this ray tracing program written in OCaml and run it on your CPU implemented on an FPGA

Split into groups to cover CPU, FPU, simulation tool, and compiler tool chain, students started by designing a RISC ISA and then built a CPU around it. You can follow the class' retrospective write-up and then dive into the GitHub pages for each of the system's components, though the commentary is mostly in Japanese. Hey, you can Google translate, right?

The original task was to run a ray-tracing demo on the FPGA-hosted processor, but the students went much further, porting Xv6, which is a Unix-like operating system intended for educational use , provided by MIT, then ran the OCaml ray tracing demo additionally. Xv6 is intended for x86, not their own ISA, so a significant amount of work went into the compiler toolchain. The obvious route would be to port LLVM or GCC, but the group decided it would be more fun to build their C89-compliant toolchain from scratch, and UCC was born!

The original processor had no MMU or interrupt handling, so it had to be added to the design as well as the simulator. One of the gang members added the extra hardware features needed to support the Unix-like operating system, producing a new processor design, which they named GAIA. The final version of Xv6 for the GAIA processor is available here. If you want to play around with it, they even made a Javascript version (using emscripten) for you to try in your browser! Blimey, and we thought our student projects were tough, let alone do this for extra credit!

Now we know what you're thinking — question number one — can it be catastrophic? We don't know yet, but here on Hackaday there's always another one around the corner who can.

A few years ago, [Takaya Saeki] and other students at the University of Tokyo received very limited instruction during their "CPU drill" class, like:

Take this ray tracing program written in OCaml and run it on your CPU implemented on an FPGA

Split into groups to cover CPU, FPU, simulation tool, and compiler tool chain, students started by designing a RISC ISA and then built a CPU around it. You can follow the class' retrospective write-up and then dive into the GitHub pages for each of the system's components, though the commentary is mostly in Japanese. Hey, you can Google translate, right?

The original task was to run a ray-tracing demo on the FPGA-hosted processor, but the students went much further, porting Xv6, which is a Unix-like operating system intended for educational use , provided by MIT, then ran the OCaml ray tracing demo additionally. Xv6 is intended for x86, not their own ISA, so a significant amount of work went into the compiler toolchain. The obvious route would be to port LLVM or GCC, but the group decided it would be more fun to build their C89-compliant toolchain from scratch, and UCC was born!

The original processor had no MMU or interrupt handling, so it had to be added to the design as well as the simulator. One of the gang members added the extra hardware features needed to support the Unix-like operating system, producing a new processor design, which they named GAIA. The final version of Xv6 for the GAIA processor is available here. If you want to play around with it, they even made a Javascript version (using emscripten) for you to try in your browser! Blimey, and we thought our student projects were tough, let alone do this for extra credit!

Now we know what you're thinking — question number one — can it be catastrophic? We don't know yet, but here on Hackaday there's always another one around the corner who can.

What's Your Reaction?